10-bit Lvds Serializer

Cobra digital pc 1000 win 7 driver. View and Download Cobra Digital PC1000 specifications online. Ultimate Web Camera. PC1000 Webcam pdf manual download.

The Serializer transmits serialized data and clock bits (10+2 bits) from the serial data output (DO±) at 12 times the TCLK frequency. For example, if TCLK is 66 MHz, the serial rate is 66 × 12 = 792 Mega-bits-per-second. The serializer output is held in high impedance until the device is fully locked to the local system clock. 10-Bit Bus LVDS Serializers. DS92LV1021A www.ti.com SNLS151F – MAY 2004– REVISED MAY 2004 DS92LV1021A 16-40MHz 10 Bit Bus LVDS Serializer Check for Samples: DS92LV1021A 1FEATURES MHz clock).

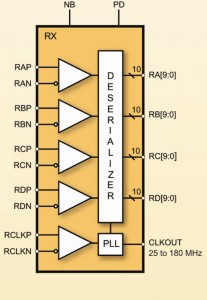

MAX9235 10-Bit LVDS Serializer - 19-0849; Rev 1; 12/07 10- Bit LVDS Serializer General Description The MAX9235 serializer transforms 10-bit-wide parallel LVCMOS/LVTTL data into a serial high-speed, low-voltage differential signaling ( LVDS) data stream. The serializer typically pairs with deserializers like the MAX9206, which receives the serial output and transforms it back to 10-bit-wide parallel data. The MAX9235 transmits serial data at speeds up to 450Mbps over PCB traces or twisted-pair cables.

Cmos 10 Bit Lvds Main Camera Board

Since the clock is recovered from the serial data stream, clock-to-data and data-to-data skew that would be present with a parallel bus are eliminated. The MAX9235 serializer requires no external components and no control signals and can lock to a 16MHz to 45MHz system clock. The serializer output is held in high impedance until the device is fully locked to the local system clock. The MAX9235 operates from a single +3.3V supply, is specified for operation from -40°C to + 105°C, and is available in a 16-pin TQFN (3mm x 3mm) package. Lane Departures Security Cameras Applications Rear View Cameras Production Line Monitoring Features ♦ Stand-Alone Serializer (vs.

SERDES) Ideal for Unidirectional Links ♦ Framing Bits for Deserializer Resync Allow Hot Insertion Without System Interruption ♦ LVDS Serial Output Rated for Point-to-Point Applications ♦ Wide Reference Clock Input Range 16MHz to 45MHz ♦ Low 31mA Supply Current ♦ 10- Bit Parallel LVCMOS/LVTTL Interface ♦ Up to 450Mbps Payload Data Rate ♦ Small 16-Pin TQFN (3mm x 3mm) Package PART Ordering Information IN- PIN- PACKAGE REF CLOCK RANGE (MHz) PKG CODE M AX 9235E TE + 16 TQFN-EP. 16 to 45 TI633-5 +Denotes a lead-free package. Note: The device is specified over the -40°C to + 105°C temperature range.EP = Exposed pad. Pin Configuration and Functional Diagram appear at end of data sheet. Typical Application Circuit MAX9235 IN TCLK INPUT LATCH PLL PARALLEL-TO-SERIAL TIMING AND CONTROL OUT+ 10 10 100Ω 100Ω LVDS PCB OR TWISTED PAIR IN+ OUT- PLL SERIAL-TO-PARALLEL OUTPUT LATCH TIMING AND CONTROL OUT REFCLK EN LOCK MAX9235 MAX9206 CLOCK RECOVERY RCLK RCLKR/F Maxim Integrated Products 1 For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.